服务内容全部包含:

高效JPEG编码器

JPEG编码使用Verilog语言编写,基于DCT变换和Huffman编码。

一、主要特点

JPEG编码器主要特点如下:

a) 自动生成JIFF头部数据;

b) 实时可编程量化表;

c) 优化计算的高速DCT变换算法;

d) 最大图片分辨率16384*16384;

e) 彩色域和Mimo域可设定;

f) 主流FPGA(Xilinx,Intel,lattice)运行时钟速率≥125MHz,实时平均编码效率优于1080P24;

g) 默认数据接口为AXI3/4,配置接口为AXI4 Lite。

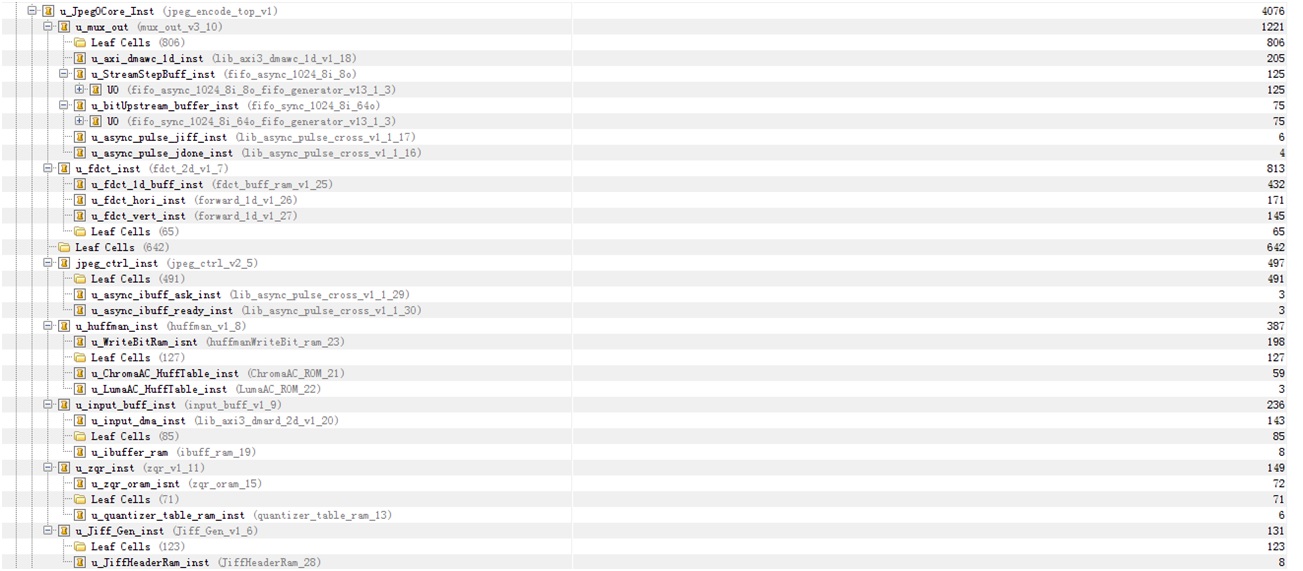

二、资源利用

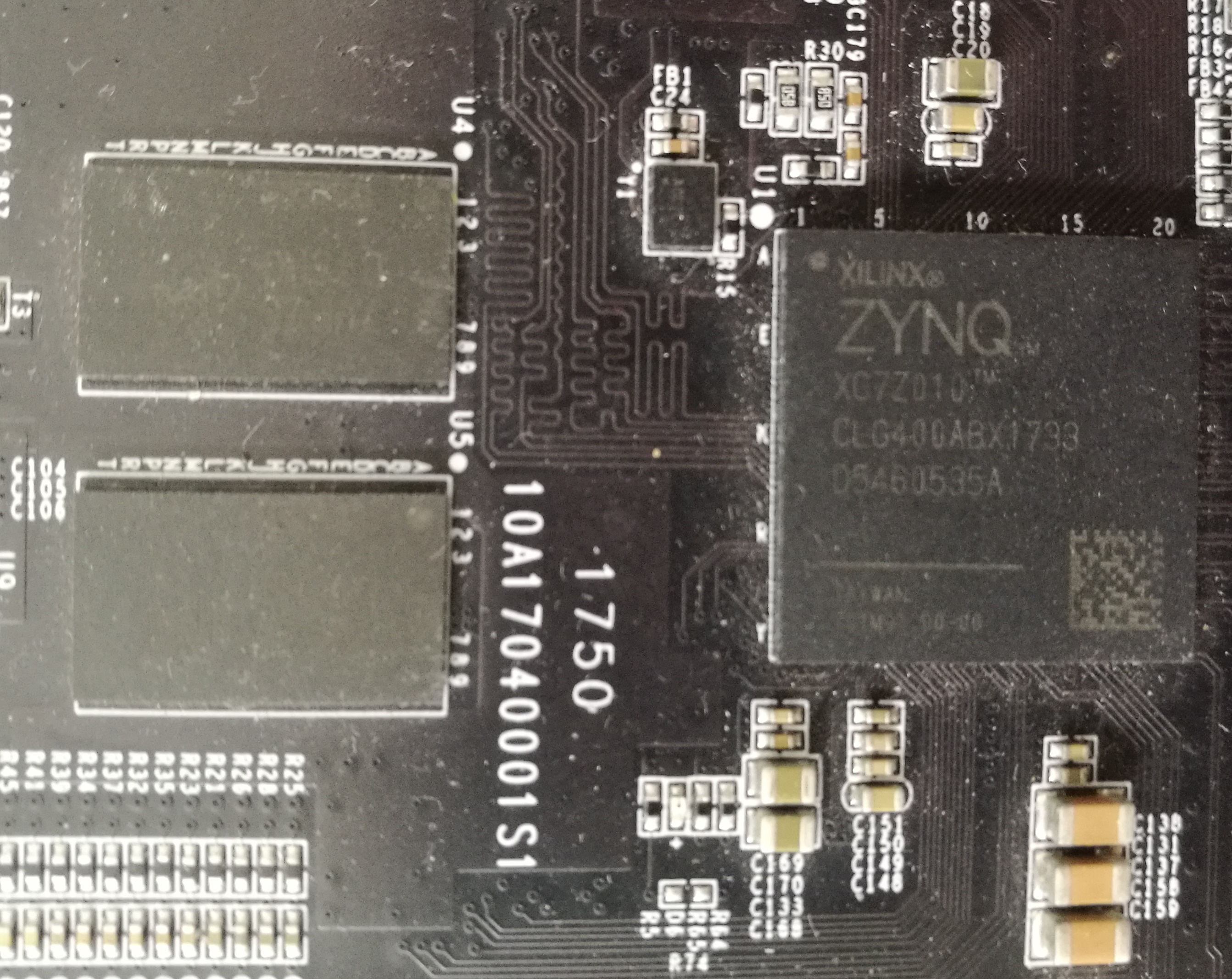

在Xilinx ZYNQ7010上实现,运行时钟150MHz,资源占用如下:

a) 逻辑资源(LUT):4076(含接口逻辑);

b) BRAM资源: RAM18-7个,RAM36-2个;

c) DSP资源:1个DSP48E。

三、技术服务

a) 可针对FPGA平台进行资源平台适配和代码优化;

b) 可定制数据和配置接口;

c) 提供黑盒或源码授权。